# ADVANCED TRANSPORT PROPULSIONS :MACHINE LEARNING SYNTHESIS FOR REAL TIME MIRRORING

- **Dr.M.Rajaiah**<sup>1</sup>, Dean Academics & HOD, Dept of CSE, Audisankara College of Engineering and Technology, Gudur.

- **Mr.B.Hari Babu<sup>2</sup>**, Assistant Professor, Dept of CSE, Audisankara College of Engineering and Technology, Gudur.

- **Ms.A.Vineetha**<sup>2</sup>, UG Scholar, Dept of CSE, Audisankara College of Engineering and Technology, Gudur.

- **Mr.I.Siva Krishna Reddy**<sup>3</sup>, UG Scholar, Dept of CSE, Audisankara College ofEngineeringand Technology, Gudur

- **Mr.B.Venkata Krishna**<sup>3</sup>, UG Scholar, Dept of CSE, Audisankara College ofEngineeringand Technology, Gudur

- Mr.A.Nagendra Reddy<sup>3</sup>, UG Scholar, Dept of CSE, Audisankara College ofEngineeringand Technology, Gudur

## **ABSTRACT:**

Major industries throught the world are being transformed by the artificial intelligence (AI) revolution. Many engineers and scientists are interested in AI because it makes correct inferences. After careful consideration, it appears that hardware- in- the-loop (HIL) emulation may choose to use this kind of modeling approach as one of the choices. In this article, a method for simulating power electronic motor drive transients for advanced transportation applications (ATAs) without a conventional circuit-oriented transient solver is proposed. To verify the realtime emulation application-specific labs, the more electric aircraft (MEA) power system is used as a case study. MLBs have used neural networks (NNs) to create component-, device-, and system-level models for diverse pieces of machinery. These models have been successfully trained in a cluster and are now being used with field-programmable gates. Based hardware platform (FPGA). The results of the MLBB emulation are then contrasted

with those obtained by PSCAD/EMTDC for the system level and SaberRD for the device level. The

which has been applied in the areas of face verification, image resolution processing, human results of the comparison revealed great consistency for modelcorrectness and high speed-up forhardware execution.

## .

#### 1.INTRODUCTION

Increasing adoption of a renovated power electronic drive system has been witnessed in the advanced transportation application (ATA) of more electric aircraft (MEA) all-electric ships (AES)traction, etc.

The reason behind these ATAs is highly related to their lower-cost ownership and substantially increased system reliability. Innovative power electronics are the fundamental enabling technology in the reduction of physical weight and fuel utilization in ATAs. Consequently, it is crucial to create hardware-in-the-loop (HIL). computation power based on the traditional electromagnetic transient (EMT) algorithms.

To be more specific, the increasingly integrated power electronic system introduces excessive system nodes into the circuit network, which results in heavy execution delays for getting the final solution. Recently, the development of artificial intelligence (AI) and its application- specific integrated circuit (ASIC) give a new possibility to represent the next-generation circuit solver. These newly developed AI neural network (NN) models are forecasting methods based on nonlinear mathematical equivalent, action recognition and natural language processing. The ideally suited hardware for the NN's inherent .

The primary difficulty with the existing HIL emulation method is the limited computing capacity provided by the old-school electromagnetic transient (EMT) techniques. To be more precise, when power electronic systems get more integrated, they add an excessive number of system nodes to the circuit network, which causes a significant execution delay in reaching the answer. A fresh opportunity to depict the next- generation circuit solver has recently arisen with the development of artificial intelligence (AI) and its application.

### 2.PROPOSED SYSTEM:

The MLBBs method can take advantage of FPGA technology for concurrent HIL simulation. This section introduces dataset processing and parameter design for NNs modeling, followed by discussions of training capabilities, hardware platform, and a comparison of RNNs. The hardware resource usage is then examined.

The most crucial components of ML training are datasets and normalization because they have a big impact on the outcomes. The datasets must include a variety of equipment operating circumstances in order to ensure the generality of the models. As an illustration, the data collection for the SiC IGBT model is used. While the ESS topology in SaberRD is identical to that on FPGA, the operating voltage and current provided by the two-quadrant buck converter are flexible enough to train the adaptable SiC IGBT ML model.

## **2.1 MODELING PARAMETERS:**

Prior to talking about the parameters, a performance- based criterion is introduced. The mean absolutes error (MAE) is an additional criterion to assess errors, and the mean squared error (MSE) is a recommended criterion for evaluation in machine learning. Their outcomes in these models are comparable, but MAE has a value that is more consistent across the entire dataset.

The two-quadrant buck converter offers a variety of inputs that can be used to train the flexible SiC IGBT ML model. While some of these working circumstances resemble thoseon FPGA, some are different. The SiC IGBT ML model is created, and it. The two-quadrant buck converter offers a variety of inputs that can be used to train the flexible SiC IGBT ML model. While some of these working circumstances resemble those on FPGA, some are different. The SiC IGBT ML model can be constructed and used for many power converter types. It is important to note that the dataset does not call for the sampling of continuous and dense data for training. The training dataset can sample with a somewhat big interval from the original dataset. Next, all of the dataMAE = n = 1 yprei – yi n = 1

## 2.2 RNNS'S TRAINING AND COMPARISON

In the field of artificial intelligence, the MAE is used as a metric to assess model efficacy because it describes errors between expectation and prediction. The NNs' predictive output, denoted as you, is comprised of three components: y, the expected

output, and n, the number of outputs. To find the best weights and least error, the training procedure is then iterative and based on the stochastic gradient descent (SGD) optimization method. The model's MAE is minimized in this work using the Adamalgorithm, the most well-liked SGD optimization algorithm. The layer size is an important parameter for NNs. The accuracy of NNs increases with the number of layers they have. The cost of hardware resources, latency, and execution time also rise considerably as the number of layers increases. Models with a single layer can be adjusted for hidden size and sequence length to fit specific application needs. As a result, all models have a default layer size of 1. The training outcomes for various pairs of hidden-size coefficients and sequence length when the layer size is 1 are evaluated using a single PMSM CRNN model, as shown in Fig. 6. (a). The hidden-size coefficient in Fig. 6(a) refers to the multiple of the hidden layer's number of neurons in relation to the input layer's number, while the sequence length refers to the number of RNN calls made by a layer. The equipment for modeling the power system's components can be found inside the circle according to the conclusion in Fig. 6(a). The values presented in this study are the standard parameters for all RNNs; the hidden size is roughly 4 times the input size, and the sequence length is 3. The intricacy of the models, however, causes them to change.

#### **3.LITERATURE SURVEY:**

RNN is displayed when the hidden-size coefficient is 4, and the sequence length is 3. (b). As can be observed, LSTM outperforms the other two RNNs; the MAE of the GRU is comparable to that of LSTM; and when the length of the sequence is short, CRNN also performs well. CRNN is the best option for the current applications since the sequence length is typically less than 4, and it imposes significantly less computing cost. A lot of time must be spent throughout NN training. Many techniques exist for improving training: 2) Varying learning rate (LR): LR should gradually decrease during training to get higher performance with fewer training epochs. 1) Data shuffling: To prevent overfitting, the data should be shuffled before delivering it to the training software. In this work, we employ both data shuffle and changing LR. Results from the model trained by shuffling the data are shown in Fig. 7(a), while those from the model trained without shuffling the data are shown in Fig. 7(b). Without data rebalancing, this model's training could have narrowed its focus and made it overfit.

Weights around the ideal weight. Traditional SG has a fixed LR, whereas the Adam algorithm has to change LR. By adjusting the starting LR, one can reduce the range of LR in the Adam algorithm. Without these techniques, the trained models might not be available or might not be very accurate. Models were trained in a cluster of 196 nodes after parameter design, NN type selection AAAA n, and training optimization technique selection. Four Nvidia V100 Volta graphics processing units (GPUs), two Intel Silver 4216 Cascade Lake CPUs, and 187 GB of memory make up each node. The MLBB models were trained using up to 8 cluster nodes. On a cluster node, training a single model only requires 6–12 hours as opposed to 12–24 hours on a personal computer (PC).

All of the CRNN models in this study FIGURE 9. The real-time ATA emulation system's hardware connection, are constructed under 1% MAE after 100 epochs, despite the fact that the NN parameters design, complexity of the modeling objects, epoch number, the training technique, and other factors can affect the MAEs during training. These models are put into the conventional simulation system. Various evaluation settings in order to test their generalizability. The models will only be used to develop system block by block on an FPGA if they pass all of these check.

TABLE 2. Hardware Resource Consumption for ML-Models in MEA

| Device         | BRAM   | DSP    | FF      | LUT     | Latency |

|----------------|--------|--------|---------|---------|---------|

| Each IGBT      | 4.27%  | 4.43%  | 0.33%   | 2.63%   | 370 ns  |

| Generator      | 4.27%  | 2.16%  | 0.21%   | 1.50%   | 520 ns  |

| Each Transf.   | 4.27%  | 4.75%  | 0.28%   | 2.29%   | 550 ns  |

| Each Rectifier | 4.27%  | 3.58%  | 0.31%   | 2.66%   | 640 ns  |

| Each Converter | 4.27%  | 5.95%  | 0.34%   | 3.02%   | 640 ns  |

| Each PMSM      | 4,27%  | 7,19%  | 0.36%   | 3.19%   | 810 ns  |

| Total Util.    | 55.51% | 68.24% | 2.76%   | 37.05%  | 820 ns  |

| Available      | 4032   | 9024   | 2607360 | 1303680 |         |

..

# **Blockdiagrams:**

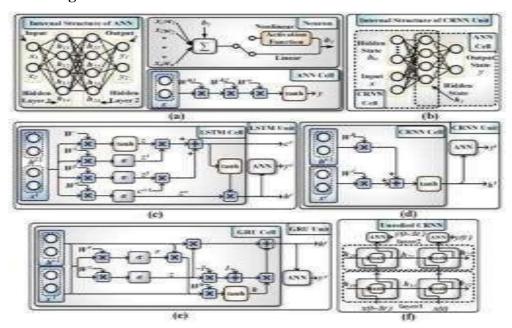

fig 1. Neural ne

twork organization: ANN, CRNN internal structure, LSTM, CRNN, GRU, and unrolled CRNN are only a fewexamples

# fig 2. Neural ne

twork organization: ANN, CRNN internal structure, LSTM, CRNN, GRU, and unrolled CRNN are only a fewexamples

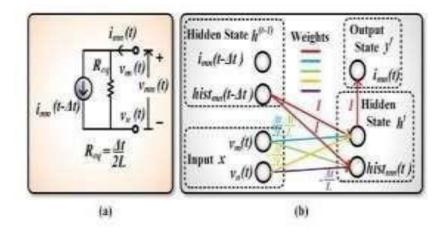

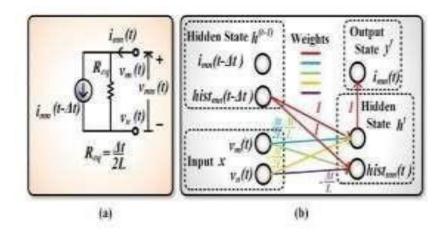

FIGURE 3. Component-level models: (a) traditional modeling schematic.

(b) component-level ML modeling schematic.

FIGURE 3. Component-level models: (a) traditional modeling schematic.

(b) component-level ML modeling schematic.

## **4.CONCLUSION:**

Conclusion VI This study suggested an MLBB- based modeling approach to accurately and efficiently simulate the transients of ATA at the component (50 ns time-step), device (50 ns time-step), and system (1.0 s time-step) levels on the FPGA platform. Finally, the correctness of various level models is examined and contrasted with offline findings from the PSCAD/EMTDC (system-level) and SaberRD (device-level) tools. These benefits apply tothe suggested approach: 1) High execution efficiency: MLBBs use matrix inversion rather than the traditional matrix solver, which significantly reduces model latency and computational complexity for each execution step. ML algorithm also causes less execution delay for nonlinear processes than the traditional iteration algorithm, and NNs are ideal for parallel execution by FPGAs. 2) Flexible modeling: despite the system's devices' differences, they can be modeled using a comparable ML framework.

ML models can be produced by the outward properties of operating devices, whereas traditional modeling methods need to halt the devices and verify internal attributes. The emulation system can be divided into hierarchical execution units based on the user's specifications. 3) High accuracy: For every model in the ATA, the error between the MLBB outputs and the original datasets is less than 1%.

The aforementioned advantages greatly increase the versatility, adaptability, and executability of MLBBs. Future studies will concentrate on real-time multi-domain modeling and simulation of ATAs based on the MLBB technique.

#### **FUTURE WORK:**

The transport sector is an important engine of growth in all economies. Governments and the private sector are investing substantially in transport infrastructure to improve mobility and connectivity to increase productivity and growth in a safe and sustainable way.

According to PWC, global transport infrastructure spending is expected to total more than \$14 trillion from 2016 to 2025. Investing in this sector not only increases economic opportunities and business development, it also boosts job creation. Policy makers and private enterprises need to explicitly harness this employment potential by investing in skills and talent development, particularly in the context of rapidly advancing technology.

A compelling benefit of strengthening skills and talent is that trained and skilled workers will be able to access scores of jobs created by the expanding transport sector

## **REFERENCES:**

- P. Wheeler and S. Bozhko, "The more electric aircraft: Technology and challenges," *IEEE Electrific. Mag.*, vol. 2, no. 4, pp. 6–12, Dec. 2014.

- B. Sarlioglu and C. T. Morris, "More electric aircraft: Review, challenges, and opportunities for commercial transport aircraft," *IEEE Trans. Transp. Electrific.*, vol. 1, no. 1, pp. 54–64, Jun. 2015.

- B. Zahedi and L. E. Norum, "Modeling and simulation of all-electric ships with low-voltage DC hybrid power systems," *IEEE Trans. Power Electron.*, vol. 28, no. 10, pp. 4525–4537, Oct. 2013.

- [4] G. Sulligoi, A. Vicenzutti, and R. Menis, "All-electric ship design: From electrical propulsion to integrated electrical and electronic power systems," *IEEE Trans. Transp. Electrif.*, vol. 2, no. 4, pp. 507–521, Dec. 2016.

- T. Liang and V. Dinavahi, "Real-time device-level simulation of MMCbased MVDC traction power system on MPSoC," *IEEE Trans. Transp. Electrific.*, vol. 4, no. 2, pp. 626–641, Jun. 2018.

## ISSN2515-8260 Volume10, Issue 02, 2023

- D. Miyashita, S. Kousai, T. Suzuki, and J. Deguchi, "A neuromorphic chip optimized for deep learning and CMOS technology with timedomainanalog and digital mixed-signal processing," *IEEE J. SolidState Circuits*, vol. 52, no. 10, pp. 2679–2689, Oct. 2017.

- [7] C. Dong, C. C. Loy, K. He, and X. Tang, "Image super-resolution using deep convolutional networks," *IEEE Trans. Pattern Anal. Mach. Intell.*, vol. 38, no. 2, pp. 295–307, Feb. 2016.

- Y. Taigman, M. Yang, M. Ranzato, and L. Wolf, "DeepFace: Closing the gap to human-level performance in face verification," in *Proc. Conf. Comput. Vis. Pattern Recognit.*, Columbus, OH, 2014, pp. 1701–1708.

- [9] S. Ji, W. Xu, M. Yang, and K. Yu, "3D convolutional neural networks for human action recognition," *IEEE Trans. Pattern Anal. Mach. Intell.*, vol. 35, no. 1, pp. 221–231, Jan. 2013.

- [10] R. Sarikaya, G. E. Hinton, and A. Deoras, "Application of deep belief networks for natural language understanding," *IEEE/ACM Trans. Audio, Speech, Lang. Process.*, vol. 22, no. 4, pp. 778–784, Apr. 2014.

#### **AUTHOR PROFILES**

**Dr.M.Rajaiah**, Currently working as an Dean Academics & HOD in the department of CSE at ASCET (Autonomous), Gudur, Tirupathi(DT).He has published more than 35 papers in, Web of Science, Scopus Indexing, UGC Journals.

# **European Journal of Molecular & Clinical Medicine**

## ISSN2515-8260 Volume10, Issue 02, 2023

**Dr.B.HariBabu**completed his masters in computer applications in ASCET Gudur JNTUA. He completed his Masters of Technology in Computer Science and Engineering, in GKCE sullurpeta JNTUA. Currently working as an Associate Professor in the department of CSE at ASCET (Autonomous), Gudur, Tirupathi(DT). His areas of interest include, Data Mining ,optimization technology , java programming.

**Ms.Alladivineetha**, as B .Tech student in the department of CSE at Audisankara College of Engineering & Technology, Gudur. He has pursuing in computer science & engineering.

**Mr. BhogyamVenkata Krishna**, as B .Tech student in the department of CSE at Audisankara College of Engineering & Technology, Gudur. He has pursuing in computer science and engineering.

**Mr.Iragala Siva Krishna Reddy**, as B .Tech student in the department of CSE at Audisankara College of Engineering & Technology, Gudur. He has pursuing in computer science and engineering

**Mr.AguduruNagendra Reddy**, as B .Tech student in the department of CSE at Audisankara College of Engineering & Technology, Gudur. He has pursuing in computer science and engineering