ISSN2515-8260 Volume04, Issue01, 2017

DESIGN AND IMPLEMENTATION OF LOW POWER VLSI DESIGN CIRCUITS **USING CAD TOOLS**

V.SANDEEP, Y.JALAJAKSHI, K.VANISREE, K.DEEPA, P.CHANDRA SHEKAR,

Assistant Professor, Assistant professor, Research Scholar Department of ECE, Assistant professor, Assistant professor,

Department of FCF.

Samskruti College of Engineering and Technology, Ghatkesar.

**ABSTRACT**

In this technology, an power densities is measuring into watts per square millimetre as a raises to alarm rates, power managements are become an importance aspects of nearly each categories of the designed & applications. Reduces the power consumptions & in excess of on chips power managements is the key challenging into deep sub-micron meters nodes as increases complex. Power managements required at a consider into extremely in the early hours designed stage. Too lower power methods will be employs at every each designed stages, for RTL (Register Transfer Level) and GDSII. These are review papers is described in the different strategy, methodology & power managements technique form lowpower VLSI circuit. In expectations challenged in that may be meets through designs as to designing lowpower higher performances circuit is also discuss. Stateof theart optimized into method at

various abstractions level in those targeting designs to lowpower digitals VLSI circuit is verified.

KEYWORD: Optimizations, LowPower, PowerDissipation, Power Managements

INTRODUCTION

energy dissipation has emerge as an essential layout parameter inside the format modern-day microelectronic circuits, particularly in portable computing and private conversation programs. on this paper, we survey optimization approach that concentrate on low strength dissipation in VLSIcircuits. Optimization at the circuits, commonplace sense, architectural and tool tiers are considered. sources power dissipation in CMOSgadgets are summarized via the following expression:

P = 1 2 C V 2DD f N + QSC VDD f N + Ileak VDD (1)

wherein P denotes the overall strength, VDDdeliver voltage, and f is the frequency of operation. the number one time period represent the powers required to price and discharge circuit nodes. Node capacitance represented by using C. The issue N is the switching pastime, i.e., the form of gate output transitions in line with clock cycle. the second time period in Eqn. 1 represents energy dissipation sooner or later of output transitions because of current flowing from the deliver to ground. This modern-day is regularly referred to as brief-circuit present day. The elementQSC represents the quantity of rate carried by means of using the quick-circuit current consistent with transition. The zero.33 term in Eqn. 1 represents static power dissipation because of leakage day I leak, device deliver and drain diffusion from parasitic diodes with bulk areas, opposite bias currents in those diodes expend strength. Sub threshold transistor currents furthermore burn up strength, in the sequel, we are able to take a look at with the three terms above as switching pastime electricity, short-circuit power and leakage cutting-cutting modern-day electricity. maximum of the optimizations described within the following sections cope with minimizing switching hobby electricity at numerous degrees of abstraction. In VLSIcircuits that use well-designed commonplace revel in-gates, switching interest power debts for over ninety% of the complete electricity dissipation [8].

104

### **CIRCUIT LEVEL**

They reviewed in optimizations that reduce switch hobby strength of man or woman not unusual feel-gates and transistors degree combinational circuits on this section

# A. complicated Gate format

Within the layout of complex gates, e.g., f = (a + b) c, selections concerning the area of man or woman transistors inside the gate can be made. for instance, in the N a part of the CMOSgate enforcing the above characteristic f, the parallel transistor pair a + b may be linked to the gate output or the transistor pushed with the aid of the usage of c may be associated with the gate output. in addition, given g = a b c, any serial ordering of a, b and c can be decided on inside the N a part of a CMOSgate imposing g. it is widely recognized that past due arriving alerts ought to be positioned in the direction of the output to decrease gate propagation postpone. but, the common energy dissipated is relying at the transition probabilities of the gate inputs and the internal node capacitances. Ordering of gate inputs could have an impact on each electricity and postpone. In [32] and [42] strategies to optimize the power and/or put off of not unusual feel-gates primarily based on transistor reordering are given, moderate improvements in electricity and put off may be acquired thru a simply apt ordering of transistors inner individual complicated gates.

# B. Transistor Sizing

Transistor sizing in a combinational gate circuit may need to have effect on circuit delay and electricity dissipation. If the transistors in a given gate are prolonged in period, then the remove of the gate decreases, however, electricity dissipated inside the gate will boom. further, the postpone of the fanin gates will boom due to multiplied load capacitance. Given a take away constraint, finding the right sizing of transistors that minimizes power dissipation is a computationally tough problem. a elegant approach to the hassle is to compute the slack at every gate in the circuit, wherein the slack of a gate corresponds to how a first rate deal the gate may be bogged down with out affecting the crucial take away of the circuit. Sub circuits with slacks extra than zero are processed, and the huges of the transistors decreased until the slack will become 0, or the transistors are all minimum duration, versions of the above technique are furnished in [42] and [3].

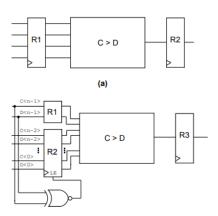

Figure 1. Precipitation Applied to a Comparator

GatedClocksLarge VLSIcircuits such as processors contain register files, arithmetic units and control logic. The register file is typically not accessed in each clock cycle. Similarly, in an arbitrary sequential circuit, the values of particular registers need not be updated in every clock cycle. If simple conditions that determine the inaction

of particular registers can be determined, then power reduction can be obtained by gating the clocks of these registers [9]. When these conditions are satisfied, the switching activity within the registers is reduced to negligible levels. The same method can be applied to "turn off" or "power down" arithmetic units when these units are not in use in a particular clock cycle. For example, when a branch instruction is being executed by a CPU, a multiply unit may not be used. The input registers to the multiplier are maintained at their previous values, ensuring that switching activity power in the multiplier is zero for this clock cycle.

#### RELATED WORK

### A. Power Dissipation

Basics Total power consumption by a CMOS device is given by,

Dynamic power or switching power is power dissipated during charging or discharging of capacitors and is described below [1] [2].

$$P \, dyn = CL^* \, Vdd2^*\alpha^* f....(b)$$

Where in CLLoad Capacitance is a function of fan out, cord period, and transistor length, Vdddeliver Voltage, which has been losing with successive manner nodes, α: interest factor f Clock Frequency, that is increasing at every successive manner node. brief-circuit electricity dissipation happens due to brief circuit contemporary (Isc) that flows while both the NMOS & PMOS gadgets are simultaneous 'on' for a brief time length and is given through the beneath equation, wherein Vth is threshold voltage, 'W' is transistor width and 'L' is transistor length figure-1 indicates the various additives answerable for energy dissipation inCMOS.

# B. Low Power Strategies

Low power designs strategies at various abstraction levels are listed in table 1.

| Design Level              | Strategies                                          |  |

|---------------------------|-----------------------------------------------------|--|

| Operating System<br>Level | Portioning, Power down                              |  |

| Software level            | Regularity, locality, concurrency                   |  |

| Architecture level        | Pipelining, Redundancy, data encoding               |  |

| Circuit /Logic level      | Logic styles, transistor sizing and energy recovery |  |

| Technology Level          | Threshold reduction, multi threshold devices        |  |

Table 1. Optimization of low power design

effective power management is viable with the aid of the use of the one-of-a-type strategies at numerous degrees in VLSI format manner. So designers want an smart technique for optimizing power consumptions in designs.

This approach is manifestly can atone for the greater capacitance introduced infeasible if a massive extensive type of format alternatives ought to because of modifications that increase concurrency. be evaluated, which is the case in synthesis. less costly adjustments that reduce the quantity of belongings electricity fashions, but, may be constructed if the very last lower degree needed to put into effect a given graph may be prolonged to circuit

fashion, module and gate library, and so forth., are steady, or at reduce the quantity of capacitance that switches. A the least, restricted in a few manner. The lower degree analysis kind of those modifications are utilized in an automated equipment can then be used to create power fashions for the tool The alterations are guided by way of using a electricity underlying structure primitives consisting of records course estimation method this is based on the parameters of the execution devices, manipulate devices, memory factors and given data/control go with the flow specification, which includes the extensive variety interconnect. The power fashions are acquired by using of operations of each kind, amount of edges, and so forth. After the characterizing the expected capacitance that could initial specification (information/manage go with the flow graph) has been switch while the given module is activated, mentioned signal transformed, the character operations want to be records are used to gain fashions which is probably greater accurate assigned control steps (scheduling) and execution gadgets than those received from the usage of random enter streams. or modules (allocation and task). If a number of What is wanted for that is an estimate of the hobby for modules, with some of electricity/put off charges, is to be had each module. hobby factors for the modules may be for enforcing the given operations sorts, an obtained from beneficial simulation over commonplace input desire of modules can bring about decrease power charges for streams, or from statistical/analytical fashions which are built the identical everyday performance.. In an trade simulation based technique techniques map operations inside the manipulate/facts drift graph in which not unusual energy costs are assigned to man or woman to useful devices, variables to registers and define the modules, in isolation from distinct modules, in the route of interconnect amongst them in terms of multiplexers and simulation, the electricity fees of the modules involved in buses. The choices made in a few unspecified time within the destiny of these methods, the given computation are added up. This method ignores which encompass the amount of hardware sharing and the correlations between the sports activities sports of different series of operations.

# VLSI DESIGN METHODOLOGIES

Performance of an IC depends on no. of conflicting parameters such as speed, power consumption, and cost and production volume. These considerations have spurred the development of a number of distinct implementation approaches ranging from High Performance, Handcrafted design o fully programmable, medium-to-low performance designs. [13]

| S.no. | Design | Advantages                 | Disadvantages                                 |

|-------|--------|----------------------------|-----------------------------------------------|

|       | Styles |                            |                                               |

| 1     | Full-  | 1. Compact                 | <ol> <li>Very time consuming;</li> </ol>      |

|       | custom | designs;                   | <ol><li>More error prone;</li></ol>           |

|       |        | <ol><li>Improved</li></ol> |                                               |

|       |        | electrical                 |                                               |

|       |        | characteristics;           |                                               |

| 2     | Semi-  | Well-tested                | Can be time consuming to                      |

|       | custom | standard                   | built-up standard cells;                      |

|       |        | cells which can be         | <ol><li>Expensive in the short term</li></ol> |

|       |        | shared between             | but cheaper in long-term                      |

|       |        | users;                     | costs;                                        |

|       |        | <ol><li>Good for</li></ol> |                                               |

|       |        | bottom-up                  |                                               |

TABLE 2. COMPARISON OF DESIGN METHODOLOGIES

Fig.2: Overview of Implementation approaches for Integrated Circuits

# ABSTRACTION LEVELS AND POWER REDUCTION TECHNIQUES

While designing an IC, the main tradeoff is Power consumption. To achieve this tradeoff a large no. of variety techniques are available at different abstraction levels. Those are as follows:

System Level: In this level, to optimize any circuit it should undergo the following process.

- Circuit Partitioning

- · Node Clustering

- Floor Planning

- Placement

- Global Routing

- Detailed Routing

From the above Methodologies, circuits can be implemented in different logic's and the performance of techniques at different abstraction levels are as shown in below table 3.

| S.No | Abstraction<br>Level | Power<br>Saving | Speed   | Error<br>Rate |

|------|----------------------|-----------------|---------|---------------|

| 1    | Logic                | 10-15%          | Hours   | 5-10%         |

| 2    | Gate                 | 15-25%          | Hour    | 10-20%        |

| 3    | Architecture         | 25-40%          | Minutes | 15-30%        |

| 4    | RTL                  | 40-70%          | Minute  | 25-30%        |

| 5    | System               | >70%            | Seconds | >50%          |

TABLE 3 COMPARISON OF POWER CONSUMPTION AT DIFFERENT ABSTRASCTION LEVEL'S

Table 4 Show the Strategies and Basic Element's which are to be optimized at different abstraction levels are shown.

| S.<br>No | Abstraction<br>Level | Strategies                                                     | Basic<br>Element's                                                  |

|----------|----------------------|----------------------------------------------------------------|---------------------------------------------------------------------|

| 1        | Logic                | Threshold<br>Reduction,<br>Multi<br>Threshold<br>Devices       | *****                                                               |

| 2        | Gate                 | Logic Style,<br>Transistor<br>Sizing and<br>Energy<br>Recovery | Logic<br>Gates,<br>Sequential<br>Element's                          |

| 3        | Architecture         | Pipelining,<br>Redundancy,<br>Data<br>Encoding                 | Register<br>Structure'                                              |

| 4        | RTL                  | Regularity,<br>Locality,<br>Accuracy                           | Function's,<br>Procedure's,<br>Processes,<br>Control<br>Structure's |

TABLE 4. STRATEGIES AND BASIC ELEMENT'S AT DIFFERENT ABSTACTION LEVELS

#### VLSI CAD TOOLS

VSLI CAD tools are basically classified into two types

- 1. Interaction Based Tools

- 2. Function Based Tools

- 1. Interaction Based Tools: These are classified as Front-End & Back-End tools.

- (A). Front-End Tools: These are mainly used for Editing the Schematic and Layout and verifying with the corresponding Simulator and Synthesizer.

- (B). Back-End Tools: These are mainly used for the purposes of Floor planning, Placement, Routing, Extracting of Schematic and Logic Diagram from Layout ERC (Error Redundancy Check), DRC (Design Rule Check), Test Vector Generator's and Format Conversion.

- 2. Function Based Tools: These are classified as

- (A) Design Capture Tools

- (B) Synthesis Tools

- (C) Analysis Tools

- (A)Design Capture Tools: These tools Are Run by using HDL's like VHDL, Verilog, System Verilog or Schematic editor.

- (B)Synthesis Tools: With this tools designer can perform synthesis at Behavioral, RTL, Physical and Logical Abstraction Levels.

- (C) Analysis Tools: These are classified as

- 1. Checkers: Design Rule Checker, Error Redundancy Checker, Ratio checker, Short Ckt Checker and power checker etc.

- 2. Verifier's: Timing Verifier, ICE/Hardware Simulator's and Formal Verifier's.

- 3. Testing Related Tool's: ATPG and DFT tools etc. Some of the Simulation and Synthesis tools are

- (a) QUESTASIM: Used for Designing, Compiling and Simulating Design's.

- (b) LEONARDO SPECTRUM: ASIC and standard cell synthesis

## **European Journal of Molecular& Clinical Medicine**

ISSN2515-8260 Volume04, Issue01, 2017

(C) Design Architect IC: for Design Capture. (d) HSPICE: Circuit simulation and verification. Some of the power analysis tools are

(a) POWERPLAY: Logic Simulation based Power estimator.

(b) POWER TIME PX: Early stage power Estimator

(c) NANO SIM: Analog Circuit Engine Simulator.

#### SOFTWARE PROGRAM

An growing fraction of packages are being implemented as embedded systems together with a hardware and a software application components. As essential a part of the functionality is within the shape of commands in preference to gates, hardware-based totally electricity estimation and optimization strategies aren't absolutely relevant proper right here. This motivates the want to keep in mind the strength intake in microprocessors from the factor of view of software program software, education-stage electricity fashions are evolved successfully for some commercial enterprise CPUs. Given the capability to assess packages in phrases of energy/strength charges, it's far viable to go looking the design area in software program power optimization, the choice of the set of rules used can impact the energy price because it determines the runtime complexity of a application. This problem is explored in [24], it's been noted that the order of commands also can have an effect on electricity because it determines the internal switching within the CPU. CAD Methodologies and approach: modern EDA tools successfully help these energy- control strategies [25], in addition they provide more electricity financial economic financial savings in some unspecified time in the future of implementation. Low power VLSI designs can be finished at diverse levels of global magazine of scientific studies in technology, Engineering and generation (ijsrset.com) 374 the layout abstraction from algorithmic and tool degrees right all the way down to format and circuit ranges.

# **CONCLUSION**

In this proposed system we extension into review of this power optimizations methods apply to the different abstractions level in like as Logic, Gates, Architectures RTL & Systems. Lastly, it can be concludes in that MultipleObject Optimizations technique is needed to achieved in LowPower VLSI designs. It is achieve through the used to ArtificialIntelligence Algorithm such as ParticleSwarm Optimizations, And Colony Optimizations, Evolutions Algorithm and etc. In this project, is abled to chosen in the optimizations technique in which is obtainable at various abstractions level.

#### REFERENCES

- [1] Kanika Kaur and Arti Noor, "techniques & Methodologies For Low electricity VLSI Designs: A evaluation" global magazine of Advances in Engineering & era (IJAET), Vol. 1,trouble 2, pp.159-165, ISSN: 2231-1963, can also 2011.

- [2] Vishal Sharma, Jitendra Kaushal Srivastava, "Designing of Low-strength VLSI Circuits using Non-Clocked logic style", international journal of advancements in studies & era (IJOART), quantity 1, Issue3, pp. 1-5, ISSN 2278-7763, August-2012.

- [3] Phani kumar M, N. Shanmukha Rao, "A Low power and high pace layout for VLSI logic Circuits the usage of Multi-Threshold Voltage CMOS technology", international journal of computer technology and records technologies (IJCSIT), Vol. 3 (3), PP. 4131-4133,ISSN: 0975-9646, 2012.

## **European Journal of Molecular& Clinical Medicine**

# ISSN2515-8260 Volume04, Issue01, 2017

- [4] massimo alioto, "extremely-low electricity vlsi circuit layout demystified And defined: an academic", ieee transactions on circuits and structures—i: normal papers, vol. fifty nine, no. 1, january 2012

- [5] Hasmukh P Koringa, Prof. (Dr.) Vipul A Shah and Prof. Durgamadhab Misra, "Estimation and Optimization of electricity dissipation in CMOS VLSI circuit layout: A review Paper", global magazine of emerging traits in electrical and Electronics (IJETEE), Vol. 1, issue.three, pp. 14-21, March-2013.

- [6] Kanika Kaur, Arti Noor, "CMOS Low energy mobile Library For digital design", international journal of VLSI layout & conversation structures (VLSICS) Vol.4, No.three, DOI: 10.5121/vlsic.2013.4305, PP. forty three-fifty one, June 2013

- [7] Srinivas Devadas, Sharad Malik, "A Survey of Optimization techniques focused on Low electricity VLSI Circuits", thirty second ACM/IEEE layout Automation conference

- [8] A. Punitha, M. Joseph, "Survey of memory, power and Temperature Optimization techniques in excessive stage Synthesis", global journal of recent tendencies in Engineering, Vol 2, No. 8, November 2009"

- [9] Valeriu Beiu, José M. Quintana, and María J. avedillo, "vlsi implementations of threshold common sense-a comprehensive survey", ieee transactions on neural networks, vol. 14, no. 5, september 2003.

- [10] Rupesh Maheshwari, Yogeshver Khandagre, Vipul Agrawal, "A survey of design technology for LowPower VLSI machine", volume No.1, trouble No.three, pg: 167-a hundred and seventy 01 July 2012